Assembly Language for the 386/486

Copyright © 1993 Maurice Castro

October 12, 2001

# Contents

| C  | ourse                   | e Overview                    | 5  |

|----|-------------------------|-------------------------------|----|

| In | $\mathbf{trod}^{\cdot}$ | uction                        | 9  |

| 1  | Pro                     | cessor Architecture           | 11 |

|    | 1.1                     | Instructions                  | 11 |

|    | 1.2                     | Integers                      | 13 |

|    | 1.3                     | Registers                     | 13 |

|    | 1.4                     | Memory Organization           | 14 |

|    | 1.5                     | Memory Hierarchy              | 18 |

| 2  | Rep                     | presentation and Organization | 19 |

|    | 2.1                     | Representation                | 19 |

|    |                         | 2.1.1 Flow Charts             | 19 |

|    |                         | 2.1.2 Pseudo Code             | 20 |

|    | 2.2                     | Program Structure             | 21 |

|    |                         | 2.2.1 The Top Down Approach   | 21 |

|    | 2.3                     | Documentation                 | 22 |

| 3  | Bas                     | ic Operations                 | 23 |

|    | 3.1                     | Basic Memory Access           | 23 |

|    | 3.2                     | Operations                    | 25 |

|    |                         | 3.2.1 Assignment              | 25 |

|    |                         | 3.2.2 Arithmetic              | 25 |

|    |                         | 3.2.3 Jumps                   | 26 |

|    |                         | 3.2.4 Alternation             | 26 |

| 4  | Con                     | atrol Structures              | 29 |

|    | 4.1                     | Pre-Test Loops                | 30 |

|    | 4.2                     | Post-Test Loops               | 31 |

|    | 4.3                     | If-Then                       | 32 |

|    | 4.4                     | If-Then-Else                  | 33 |

|    | 15                      | If Then Fleelf Flee           | 24 |

2 CONTENTS

|          | 4.6  | Switch                                    | 35      |

|----------|------|-------------------------------------------|---------|

| 5        | Sub  | routines - Introduction                   | 37      |

| 6        | Add  | dressing Techniques                       | 39      |

|          | 6.1  | Addressing Modes                          | 39      |

|          |      | 6.1.1 Direct Addressing                   | 39      |

|          |      | <del>-</del>                              | 39      |

|          |      |                                           | 40      |

|          | 6.2  |                                           | 42      |

|          | 0    |                                           | $4^{2}$ |

| 7        | Sub  | routines - Advanced                       | 47      |

|          | 7.1  | Parameter Passing                         | 47      |

|          |      |                                           | 47      |

|          |      |                                           | 48      |

|          |      | 7.1.3 Pass by Value and Pass by Reference | 50      |

|          |      |                                           | 51      |

|          |      | 9                                         | 51      |

| 8        | Dat  | a Structures                              | 57      |

| _        | 8.1  |                                           | 57      |

|          | 8.2  |                                           | 58      |

|          | 8.3  |                                           | 60      |

|          | 8.4  |                                           | 60      |

|          | 8.5  |                                           | 61      |

| 9        | Bloc | ck Structured Languages                   | 63      |

| <b>A</b> |      |                                           | 67      |

| A        |      | $\boldsymbol{v}$                          |         |

|          |      | 9                                         | 67      |

|          |      |                                           | 69      |

|          | A.3  |                                           | 70      |

|          |      | ·                                         | 70      |

|          |      | A.3.2 Operands                            | 71      |

|          |      | A.3.3 Comments                            | 71      |

|          |      | A.3.4 Expressions                         | 72      |

|          |      | A.3.5 Assembler Directives                | 72      |

|          |      | A.3.6 Memory References                   | 74      |

| В        | Inst |                                           | 77      |

|          | B.1  | Layout                                    | 77      |

|          |      |                                           | 77      |

|          |      | B.1.2 Type & Compatibility                | 77      |

| CONTENTS | 3 |

|----------|---|

|          |   |

| B.1.6 Flags      |

|------------------|

| B.2 Instructions |

4 CONTENTS

# Course Overview

This course aims to provide the student with the skills required to program in assembly language. The 386 processor has been chosen because it is common and commercially relevant. Although this course will concentrate on the 386 processor, many of the skills acquired will have wider application.

The course will cover the following major topics:

- 386 architecture

- Instructions

- Integers

- Register Set

- Memory Organization

- Memory Hierarchy

- Flow Charts and Pseudo Code

- High and Low Level Concepts

- Flow Chart Elements

- Pseudo Code Elements

- Top Down Approach

- Documentation

- Basic Operations

- Arithmetic

- Jumps

- Alternation

6 Course Overview

- Control Structures

- Pre-Test Loops

- Post-Test Loops

- If-Then

- If-Then-Else

- If-Then-ElseIf-Else

- Switch

- Subroutines (introduction)

- Call and Return

- Addressing Techniques

- Indexing

- Indirection

- Pointers

- Subroutines (advanced)

- Pass by Register

- Pass by Stack

- Pass by Reference

- Pass by Value

- Returning Results

- Stack Frames

- Data Structures

- Vectors

- Arrays

- Records

- Dope Vectors

- Trees

- Block Structured Languages

- Scope

- Implementation

The course assumes a familiarity with at least one high level language. The majority of the examples using high level languages are written in the 'C' programming language. When 'C' does not have an appropriate language concept then the Pascal language will be used.

# Introduction

A knowledge of assembly language programming is useful in many areas of computer science. Key among these areas are program optimization both at the user and compiler levels, code generation for compilers, and interfacing hardware.

A processor executes 'machine code'. Assembly language has a one-to-one mapping between its instructions and machine code instructions.

Although it is likely that many students will not be writing compilers or device drivers, all programmers should have an interest in the efficiency of the code they write. An understanding of the low level implementation of the code written in a high level language assists the design of programs in high level languages when speed is required.

With the improvement of compiler technology it is no longer necessary to write routines in assembly language to obtain good performance. However, it is still possible to replace critical routines in a program with carefully constructed assembly language programs to give peak performance. Typically these assembly language routines will reflect some additional knowledge about the problem that cannot be made available to the compiler.

10 Introduction

# Chapter 1

# Processor Architecture

The Intel 386 and 486 processors are closely related. The 486 includes an internal cache, a few additional instructions, and a floating point unit. The differences between the processors mainly concern the systems programmer as the most significant differences relate to cache management and bus locking.

#### 1.1 Instructions

Assembler instruction sets may be divided into categories by varying criteria. Typically the divisions are based on the type of operation, privilege levels, and the type of arguments.

Some of the types of operations are:

Flow of Control Instructions that may cause a change in the order of execution of instructions in a program. For example: Jumps, Conditional Jumps, and Subroutine Calls

**Integer** Instructions which manipulate integers. For example: arithmetic instructions and logical instructions on integers.

Floating Point Instructions that manipulate floating point values. For example: arithmetic instructions and logical instructions on floats.

Input Output Instructions that manipulate the IO address space.

**String** Operate on variable length vectors of similar items. For example: Memory Copying, and String Compares.

Divided by privilege:

- **Non-Privileged:** Non-Privileged instructions may be executed by any process. Typically this group of instructions include arithmetic, logical, and most flow of control instructions.

- **Privileged:** Privileged instructions must be executed by processes running at an appropriate privilege level and may include input output instructions, instructions which alter the privilege level, and instructions related to external events (eg. interrupts).

Using argument types:

- **Memory to Memory:** Operations which take an argument from memory, transform it, and record the result in memory.

- **Memory to Register:** Operations which take an argument from memory, transform it, and record the result in a processor register.

- **Register to Memory:** Operations which take an argument from a processor register, transform it, and record the result in memory.

- **Register to Register:** Operations which take an argument from a processor register, transform it, and record the result in a processor register.

and in a segmented architecture:

- **Single Segment:** For arithmetic or logical instructions: Instructions which take data from one segment, and transform it. The result may either be left in a register or the result may be written into the same segment as the source.

- For instructions which control the order of execution of a program: Instructions which may cause control to be transferred to code in the same segment.

- Multi Segment: Instructions that either transfer data between segments, or may cause code to be executed in another segment.

The 386/486 has a segmented architecture which supports the majority of the classes of instructions described above. A key feature of the architecture of the 386/486 is that, except for string instructions, the 386/486 does **not** support **memory to memory** operations. This implies that moving data from one location to another typically involves a memory to register move followed by a register to memory move. Although this may seem to be inefficient, but it can be easily shown that there are few occasions where the optimal coding of an algorithm includes memory to memory operations. Typically the result of an operation is used in the next phase of the program, in addition to being stored in memory. By retaining the result in a register the result is readily available for subsequent operations.

1.2. INTEGERS

### 1.2 Integers

The 386/486 supports 3 sizes of integers: 8 bits, 16 bits and 32 bits. The GNU As assembler defines the sizes as byte (8 bits), word or short (16 bit), and int or long (32 bit).

The 386/486 uses a **little endian** encoding of its integers. In a little endian system the low order byte is stored at the low address in memory. A big endian system stores the high order bits at the low address. (figure 1.1)

The hexadecimal number 5A4B3C2D may be represented in a computer's memory in two ways:

Little Endian:

Big Endian:

Figure 1.1: Big and Little Endian Numbers

The size of the operand of an instruction is determined by appending either a 'b' (8 bit), 'w' (16 bit), or an 'l' (32 bit) to the mnemonic.

The GNU As assembler uses the conventions of the 'C' programming language to represent numbers. Hexadecimal numbers are prefaced by  $\mathbf{0}\mathbf{x}$ , octal values by  $\mathbf{0}$  and decimals begin with any digit other than zero.

### 1.3 Registers

The 386/486 is unusual among the current generation of microprocessors as it is not a general register processor. Specific registers on the 486 are dedicated to performing specific functions. This is unusual as it increases the difficulty in optimizing code, often requiring that information be shuffled between registers or out to memory before performing an operation.

The term 'general register' has several meanings. When this term is applied to the 386/486 it is taken to mean one of the set of registers %eax, %ebx, %ecx, and %edx. In wider usage 'general register' implies that the processor does not have registers tied to specific functions. However, the registers on a 386/486 are assigned specific functions for given operations, implying that the 386/486 is not a 'general register processor'.

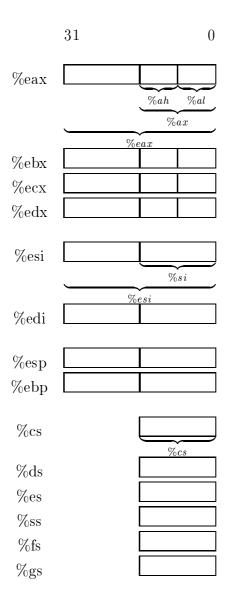

The register set of the 386/486 may be accessed in 8 bit, 16 bit and 32 bit size units. The names of the major units and an example of deriving the subunits names are shown in figure 1.2.

The registers are named according to function. The general registers are %eax, %ebx, %ecx, and %edx. They are known respectively as the accumulator, base register, count register and data register. The index registers %esi and %edi are known as the source index register and the destination index register. The pointer registers %ebp and %esp are called the base pointer and the stack pointer. The segment registers %cs, %ds, %es, %ss, are known as the code segment register, the data segment register, the extra segment register, and the stack segment register. The two additional segment registers %fs and %gs are not named.

Although specific functions are assigned to the general registers and the indexes for a few functions, for other operations they may be used interchangeably.

In addition to these registers the 386/486 has a **flag register**. This register contains a set of bits which are set according to changes in the state of the processor, and arithmetic operations.

The flag register known as **eflags** and the meanings of its bits are illustrated in figure 1.3.

### 1.4 Memory Organization

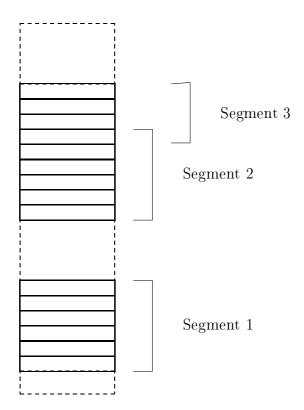

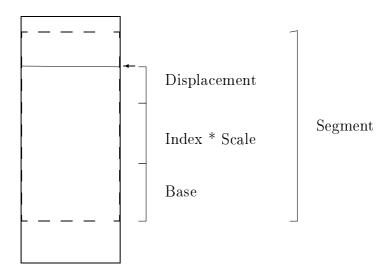

Each address in the 386/486 consists of 2 parts: segment and offset. The segment component of the address is loaded into a segment register, and instructions either explicitly mention a segment register, or implicitly use a segment register when accessing memory. The offset component specifies the distance into the segment of the memory location that is to be referenced. Figure 1.4 shows the most general representation of segmentation.

A segment is a contiguous region in memory. Segments may be disjoint or overlap other segments. In addition a segment may be a subset or superset of other segments. A segment is defined by a base, an extent and a set of rights that users of the segment may exercise.

For simplicity the examples and exercises given in this course will be conducted in '32 bit flat mode'. This is the Intel terminology for a 386/486 processor where all the segment registers have been loaded with descriptors for the complete logical address space of the system. The programmer perceives the memory as a 4 Gigabyte contiguous array of bytes. Offsets, relative to any segment, map to the same location and value in memory. Offsets, in this mode, are equivalent to the absolute addresses.

Figure 1.2: The 386/486 register set

31

####

AC Alignment Check

VM Virtual 8086 Mode

RF Resume Flag

NT Nested Task Flag

IOPL I/O Privilege Level

**OF** Overflow Flag

**DF** Direction Flag

IF Interrupt Enable Flag

**TF** Trap Flag

SF Sign Flag

**ZF** Zero Flag

AF Auxiliary Carry Flag

**PF** Parity Flag

CF Carry Flag

Figure 1.3: The EFLAGS register

Figure 1.4: Segmentation

## 1.5 Memory Hierarchy

For the application programmer using an assembler there exists a two stage memory hierarchy: Registers and Main Memory. Access to registers is significantly faster than access to main memory. However, there are a strictly limited number of registers available to the programmer. By storing frequently used values in registers a program's execution time may be reduced significantly.

# Chapter 2

# Representation and Organization

A computer program is a specific representation of an algorithm written in a programming language. The abstraction - algorithm - may be expressed in many ways. Two will be considered in this chapter: Flow Charts and Pseudo Code. The balance of the chapter will be devoted to describing the structure of programs and documentation.

### 2.1 Representation

#### 2.1.1 Flow Charts

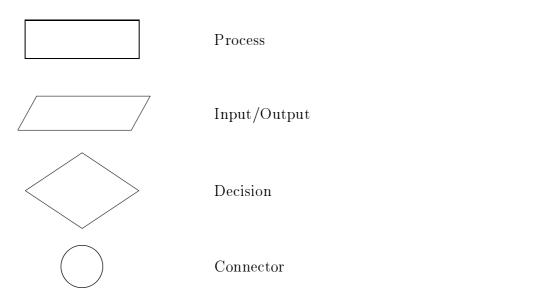

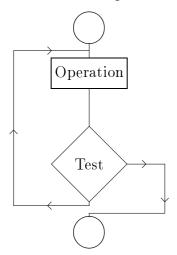

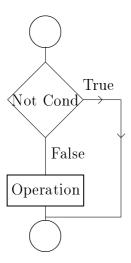

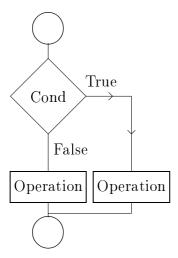

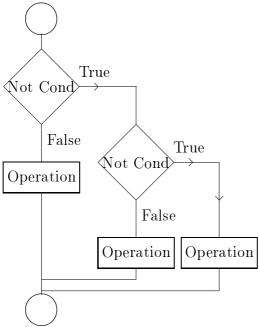

The flow chart is a method of pictorially representing an algorithm. It represents the 'flow of execution' or the 'sequence of operations' in a codified form. The basic elements of a flow chart are shown in figure 2.1. Arrow heads are used to represent the path through the chart, however, in the absence of arrows, it is assumed that vertical lines are traversed in the downward direction.

In recent years the flow chart has come to be regarded as a poor method of representing algorithms. Some of the reasons for this are:

- A flow chart can become too complex to be easily interpreted.

- A flow chart does not clearly distinguish between the structural elements of a high level language. (do loops, while loops, for loops, and conditionals are all represented by the same construct in a flow chart)

- The majority of programmers no longer work in assembler.

For the assembly language programmer the majority of these reasons are not valid. The complexity of a flow chart can be managed by the person drawing the flow chart. Problems can be broken down into independent subsections of manageable size, flow charts can be drawn for these parts and a flow chart can be drawn to show how the subsections should be executed. The majority of assembly

Figure 2.1: The elements of a flow chart

languages support only the structural elements that may be represented easily in a flow chart.

#### 2.1.2 Pseudo Code

Pseudo code is a form of structured English used to represent algorithms. Keywords are used with descriptions of actions and conditions to form a representation of an algorithm. Pseudo code is more efficient for representing algorithms than English alone, as the narrative description is too verbose, and often ambiguous.

The keywords used in Pseudo Code are typically:

- start ... stop

- if ... then ... else

- repeat ... until

- while ... do

Indentation is used to group operations, and comments are enclosed by '{' and '}'.

### 2.2 Program Structure

An algorithm in its most abstract form describes the steps in performing an operation without being concerned with the detail of a particular implementation. This is a **high level** view of a problem. A **low level** view consists of the details required for a specific implementation. Assembly language programming consists of implementing high level concepts in a low level representation. To assist in this process a **Top Down Approach** may be taken.

Assembly language programming requires strict attention to the structuring of programs. If the structure of programs is ignored then maintenance and debugging are made more complex. In addition, the readability of the program code is reduced.

### 2.2.1 The Top Down Approach

The top down approach consists of breaking a problem up into parts. The parts are broken up into smaller components until a sufficiently simple task is found, such that it can be implemented in a straight forward manner in the application language. This approach is also known as **Stepwise Refinement**.

The advantages of this approach are that it allows the programmer to solve manageable problems and then connect these solutions to solve a larger problem. If a fault is discovered in one of the components of the solution then only a subset of the components of the program needs to be examined and corrected. In addition if another programmer needs to modify the existing code then he/she need only understand the abstract meanings of the lower level modules, so that they can give attention to the area requiring modification without requiring full understanding of the details of the complete program.

#### 2.3 Documentation

Programs are documented both internally and externally. Internal documentation consists of **comments** in the program code. A comment describes the purpose of a piece of code with relation to the problem, not what the code does at a low level. For example the comment "adds one to register EAX" is considerably less useful than the comment "setup to examine next array element" although they both describe the line of code:

addl \$1, %eax

The C commenting style /\* ... \*/ is used in GNU as.

External documentation consists of a description of how the program works in abstract terms (an algorithm), notes about any short comings or limitations of the program, and details of unusual or in-obvious features of the code.

Both internal and external documentation are required to fully document a program. In assembly language programming, good documentation practices are required as, often, the structure and meaning of a piece of code cannot be easily determined from the code itself.

# Chapter 3

# **Basic Operations**

Imperative programming languages support several fundamental classes of operations. This chapter discusses a subset of the operations available on the 386/486 divided into four classes: assignment, arithmetic, jumps and alternation. The definitions of the four classes are:

**Assignment** - Storing values.

**Arithmetic** - Operations on numbers.

**Jumps** - Causing the executing of an instruction other than the instruction immediately following the current instruction.

**Alternation** - Causing the executing of an instruction other than the instruction immediately following the current instruction based on some condition.

However, before discussing the basic operations, the concepts of values and addresses are introduced and the syntax for the GNU As assembler for simple accesses to memory is covered. The concepts of indexing and indirection will be dealt with in chapter 6.

### 3.1 Basic Memory Access

A colorful metaphor used for the memory of a computer is a bank of pigeonholes where letters are placed for collection by guests at a hotel. Each pigeonhole has a room number on it to uniquely identify it to the clerk at the desk, and it has space for only one message.

Using this metaphor, the address of a memory location is the room number. The address is unique in the computer. The contents of a memory location or its value, is the message contained within the pigeonhole. As only one message can fit at a time, a new message must displace any message that is already there.

The metaphor can be further extended if the clerk is allowed to write, next to the room number on the pigeonholes a number of names. This is similar to the concept of labels. Hence Mr Smith can get his message, by saying 'I am Mr Smith may I have my message please' or 'The message for room 101 please'.

An example of a short assembly language program:

```

start:

movl d1, %eax    /* Get the data value */

addl d2, %eax    /* Add the value of data2 to data1 */

addl $2, %eax    /* Add 2 to the sum */

movl %eax, 100    /* Store the result at location 100 */

jmp exit

s1:

d1:    .long 4

d2:    .long 5

```

This short assembly language program illustrates the concepts of using and declaring labels, using addresses, and constants. The label d1 is assigned to a long integer which initially contains the value 4. d2 is assigned to a long integer which initially contains the value 5. The result of the arithmetic operations is placed at address 100. It is also clear that if the program is run before the contents of d1 or d2 are changed then the result stored at location 100 will be 11.

The declaration of a label under GNU As consists of a name followed by a colon. Several labels may refer to the one location. Thus in the above example s1 is a synonym for d1.

Labels beginning with an 'L' are local labels and are not visible at link time. In addition there are ten local symbol names '0' to '9'. These are reusable within a program, and references may be made to the nearest forward ('f') or backward ('b') reference by writing labelf or labelb, respectively.

In hand coded assembler, the practice of using local symbols and local labels is strongly discouraged as it makes assembly code significantly more difficult to read and debug. Macros are the single exception to this rule. Local symbols simplify the writing of macros by allowing relatively context insensitive macros to be written which contain loops.

In addition to their significant role in macros, local symbols and local labels are typically heavily used in the output of compilers.

Memory is declared and initialized using the assembler directives .byte, .word, .int, and .long where bytes are 8 bits in length, words 16 bits, and integers and longs 32 bits in length. The declarations must be followed by a list of numbers, and these numbers are placed into memory to initialize the memory locations. If no numbers follow the declaration then, no space is reserved by the declaration.

The following code fragment illustrates the reservation of memory and initialization of memory locations:

3.2. OPERATIONS 25

```

.long 5 /* reserves 32 bits and places 5 in it */

.long 5, 7 /* reserves two longs and places 5 and 7 in them */

.byte 4, 6 /* reserves two bytes and places 4 and 6 in them */

.long /* reserves no space */

```

Strings may be stored in memory using the .ascii and .asciz assembler directives. These directives store a series of bytes with the values of the string that follows the directive into memory. The .asciz form appends a byte containing a zero to the end of the string.

The following two lines of code are examples of the use of the .ascii and .asciz directives.

```

.asciz 'A string terminated by a NULL''

.ascii 'A string not terminated''

```

Immediate constants are formed by prepending a '\$' to a label or a value. This construct may be used to get the address of a label, typically before passing that address to a subroutine. For example:

```

movl $10, %eax /* Copy 10 to EAX */

movl $s1, %eax /* Copy the address of label s1 into EAX */

```

A final note, GNU As uses the AT&T format for instructions. This format places the destination in the rightmost operand. The majority of 386/486 assemblers use the Intel format which places the destination in the leftmost operand.

### 3.2 Operations

### 3.2.1 Assignment

The fundamental assignment operation provided by the 386/486 is the **mov** instruction. This operation copies data from source to destination without altering the source or the flag registers.

The following lines of code illustrate the syntax of assignment operations under GNU As.

```

movl 10, %eax /* Copy contents of address 10 into EAX */

movl $10, %eax /* Put the value 10 into register EAX */

movl %ebx, %eax /* Copy the value of EBX to EAX */

movb %edx, 10 /* Copy the low byte of EDX to location 10 */

```

#### 3.2.2 Arithmetic

The 386/486 supports a wide range of arithmetic and bitwise logical operations on integers. The operations include: add, bitwise and, divide, integer divide, integer multiply, multiply, negate, bitwise not, bitwise or, rotate, shift, subtract and bitwise exclusive or. The format for these operations is typically: op src, dst

where the result is calculated by  $dst = dst \ op \ src$ . The most notable exception to this formating is the integer multiply instruction which has a three-operand form. A detailed description of the multiply instruction is found in appendix B. A set of two-operand form examples are below:

```

addl 10, %eax /* Add the contents of address 10 to EAX */

subl $10, %eax /* Subtract 10 from EAX */

xorl %ebx, %eax /* EAX = EAX xor EBX */

addb %edx, 10 /* add the low byte of EDX to location 10 */

```

#### **3.2.3** Jumps

The 386/486 supports a large number of types of jumps and subroutine calls. The five forms are defined as:

**Absolute** - Jump to a specified location

**Relative** - Jump to a location calculated by adding a signed offset to the address of the instruction following the jump instruction.

**Intersegment** - Jump to a location in another segment.

**Indirect** - Jump to a location given in either a register or a memory location.

**Indirect Intersegment** - Jump to a location defined by a segment offset pair given in memory location.

In this book we will be developing only single code segment programs, and the assembler will treat the jump or call mnemonic as a relative jump, or call of a sufficiently large magnitude.

```

jmp exit /* Jump to the label exit */

call subone /* call the function beginning at subone */

are examples of the syntax of relative jumps. Jumps to absolute addresses may be

formed by prefixing the address with a '*'. Otherwise, the assembler will choose

program counter relative addressing.

```

#### 3.2.4 Alternation

The 386/486 implements alternation through the use of conditional jumps. The conditions used to determine whether to jump or not are based on combinations of bits in the EFLAGS register. It is necessary for the programmer to ensure that the appropriate bits are set in the EFLAGS register before using the conditional jump instruction to test for the condition. A typical example would be:

```

cmpl $0, %eax /* Set flags in EFLAGS */

je zero /* Jump to zero if EAX equals zero */

jmp nonzero /* Not zero, jump to nonzero */

```

The compare instruction (cmp) performs the subtraction EAX - 0. Setting the required flags in EFLAGS but otherwise not altering any registers. Je tests the zero flag (zf) in EFLAGS, if the flag is set a jump occurs to the label zero.

The **test** and **cmp** operations set flag bits without altering either memory or general register contents. Arithmetic and bitwise logical operations alter both the flag bits and the destination of the operand of the instruction. As these operations affect the EFLAGS register conditional jumps may be used to detect the results of these operations.

The operations mov, jmp and call do not typically affect flag bits.

A notable feature of the architecture of the 386/486 is that all conditional jumps are implemented as relative jumps.

# Chapter 4

# Control Structures

This chapter will illustrate typical control structures found in assembly language programs. The control structures shown in this chapter may be nested, but they should not be overlapped, when writing structured programs.

Although there are several methods of implementing the conditional structures, only one method is shown and described as an example. Provided only one method of implementing conditionals is used within a program, it is possible to construct structured programs which are easily readable.

## 4.1 Pre-Test Loops

Pre-test loops test that a condition is satisfied before entering the body of the loop. This class of loop is represented by the  $while \dots do$  in pseudo code and the while loop in C.

```

while z not equal 0 do

a = a + a

z = z - 1

```

# 4.2 Post-Test Loops

Post-test loops test that a condition is satisfied after executing the body of the loop. This class of loop is represented by the  $repeat \dots until$  in pseudo code and the  $do \dots while$  loop in C.

```

repeat a = a + az = z - 1until z equal 0

```

```

ploop:

movl a, %eax /* let a equal a + a */

addl %eax, a

dec z /* subtract 1 from z */

cmpl $0, z /* test if z is zero */

je eloop

jmp ploop

eloop: /* exit the loop */

```

## 4.3 If-Then

The **If** ... **Then** conditional may be expressed in assembly language by testing for the negation of the condition. If the negation is true then the consequence - the then clause - is skipped.

if

$$z$$

equal 0 then  $a = 1$

```

cmpl \$0, z /* test if z is zero */

jne ethen

movl \$1, a /* let a equal 1 */

ethen: /* exit the conditional */

```

33

## 4.4 If-Then-Else

The **If** ... **Then** ... **Else** conditional is expressed in assembly language as a test for the condition: If the condition is met, then a jump to the 'true' code is made, otherwise the 'false' code is executed.

```

if z equal 0 then a = 1 else a = 2

```

#### 4.5 If-Then-ElseIf-Else

The  $\mathbf{If} \dots \mathbf{Then} \dots \mathbf{Else} \mathbf{If} \dots \mathbf{Else}$  conditional is a combination of the techniques for  $\mathbf{If} \dots \mathbf{Then}$  and  $\mathbf{If} \dots \mathbf{Then} \dots \mathbf{Else}$ .

```

if z equal 0 then

a = 1

elseif z equal 1 then

a = 2

else

a = 3

/* test if z is zero */

cmpl $0, z

jne eif1

movl $1, a

/* let a equal 1 */

jmp eelse

/* test if z is one */

eif1:

cmpl $1, z

jne else

movl $2, a

/* let a equal 2 */

jmp eelse

/* let a equal 3 */

movl $3, a

else:

/* exit the conditional */

eelse:

```

4.6. SWITCH 35

## 4.6 Switch

The switch or case statement may be implemented in two ways: the first is to use the **If** ... **Then** ... **ElseIf** ... **Else** construct (see Section 4.5). The second method is to use a jump table. A vector of jump addresses is calculated for each possible input value, and the input values are used as an index into the table. This technique provides quick execution. This technique is similar to that used for dope vectors (see Section 8.4).

# Chapter 5

## **Subroutines - Introduction**

The subroutine is the primary mechanism used in structured programming to allow the division of large programs into more managable smaller parts. This chapter will introduce the concepts of a subroutine, and a 'process' or 'system' stack.

A subroutine is defined as a section of program code which may be invoked with a set of parameters, perform an action and which may return a result.

The stack data structure is comprised of a list of elements which may only be accessed from one end. There are two operations defined over a stack. The first operation is PUSH, this inserts an element at the head of the stack. The second operation POP, removes an element from the head of the stack. The 'system' or 'process' stack is provided by the operating system, and it is operated on by processor operations that use a stack. The operations **push** and **pop** are provided by the 386/486, and operate on the register %esp, also known as the stack pointer.

The system stack on the 386/486 grows downwards in memory. Each time an item is pushed onto the stack the stack pointer is decremented. As items are removed from the stack the stack pointer is incremented.

The 386/486 provides two operations to support subroutines. The first operation CALL (call) causes the address of the instruction following the call instruction to be pushed onto the system stack, and control to be passed to the address contained in the operand of the call instruction. The RETURN instruction (ret) pops an address of the stack and transfers control to that address.

The intrinsic mechanisms provided by the processor allow for *nested* subroutine calls. Nested subroutine calls are calls on subroutines from within a subroutine. The stack provides a history of the return addresses of the subroutine calls.

Figure 5.1 ilustrates the basic stack subroutine relationship for the following program assembled into addresses  $1000_{10}$  to  $1023_{10}$ .

Figure 5.1: Nested Subroutines and the System Stack

# Chapter 6

# Addressing Techniques

Memory may be referred to by 3 distinct methods known as addressing modes: direct, indexed and indirect. These modes may be combined to form more complex addressing mechanisms. This chapter will define the 3 addressing modes and each mode's availability on the 386/486, and relate the concepts of non-direct addressing to pointers in high level languages.

## 6.1 Addressing Modes

### 6.1.1 Direct Addressing

Direct addressing was introduced in section 3.1. Direct addressing is the simplest mode. Essentially direct addressing returns the value found in the memory location specified in the instruction.

## 6.1.2 Indexed Addressing

Indexed addressing takes a start address and an offset, and returns the contents of the memory location with the address resulting from the addition.

The 386/486 supports indexed addressing using registers to represent the base address and the index. The AT&T syntax for indexed memory references is:

segment: disp(base, index, scale)

The index index is multiplied by the scale factor scale and summed with the displacement disp and the offset base to give the address of the memory location relative to the segment segment. (See figure 6.1). In addition to the restriction requiring base and index to be registers, scale is required to have only the values 1, 2, 4, 8 or none.

The syntax of indexed access may be explicitly written as:

$$\left\{ \begin{array}{c} \%cs \\ \%ds \\ \%es \\ \%es \\ \%fs \\ \%gs \end{array} \right\} : \left\{ \begin{array}{c} No\ Displacement \\ 8-Bit\ Displacement \\ 32-Bit\ Displacement \end{array} \right\} \left( \left\{ \begin{array}{c} \%eax \\ \%ebx \\ \%ecx \\ \%edx \\ \%edx \\ \%edx \\ \%edi \\ \%edi \\ \%ebp \\ \%esp \end{array} \right\}, \left\{ \begin{array}{c} 1\\ 2\\ 4\\ 8 \end{array} \right\} \right)$$

The effective address of the memory location is calculated using the formula:

If the segment modifier is not included then the instruction uses the default segment. If the displacement is not included then a displacement of zero is assumed.

Not all arguments of the index syntax are required to be present. Valid forms of the index syntax are:

(base, index, scale) Complete form

(base, index) Scale defaults to 1

(base) Index defaults to 0

(,index,scale) Base defaults to 0

(, index, ) Base defaults to zero and scale defaults to 1

### 6.1.3 Indirect Addressing

Indirect addressing consits of extracting the address of the destination location from the location named in the instruction. Thus a location contains the address of the location containing the required value.

Figure 6.1: Indexed Addressing

| Address                      | Memory |               |

|------------------------------|--------|---------------|

| 1000<br>1004<br>1008<br>1012 | 2008   | $\rightarrow$ |

| 2000<br>2004<br>2008<br>2012 | 45     | <b>←</b>      |

If location 1004 is accessed indirectly the value returned will be 45 as location 1004 contains the address of location 2008 which contains the value 45.

Figure 6.2: Indirect Addressing

This is ilustrated in figure 6.2.

The 386/486 provides minimal support for indirect addressing. Specifically, it is available for mov and jump commands, however, only moves to and from the register %eax are supported.

Some versions of the GNU As assembler do not correctly support access via indirect addressing. Practical work in this course will not use indirect addressing.

#### 6.2 Pointers

In a high level language, a pointer is a variable that contains an identifier that allows access to either a data item or a procedure. Pointers are typically composed of the address of an object.

The assembly language concept of non-direct access is similar. The address of an item is used to refer to the item. This concept can be extended to describe each element of an object as a data item at an offset from the base of the object.

### 6.2.1 'C' to Assembler Examples

Several examples of 'C' programming constructs will be presented with translations into assembly language showing how non-direct access may be used to implement the constructs of a high level language, and how indexing construct in assembly language may be used.

#### Arrays

$\mathbf{C}$

```

int array[10];

/* ... */

array[4]++;

```

6.2. POINTERS 43

#### Assembler

```

array: .fill 10, 4, 0

/* ... */

movl $4, %eax

incl array(,%eax,4)

```

The array consists of 4 byte objects. Ten sets of 4 byte objects initialized to zero are created by the assembler directive .fill. The register %eax is loaded with index value 4 and the operation is performed after indexing into the array.

The following routine performs a similar task except on character size objects. To take account of the size change it is necessary to alter both the size of the memory operand and the scale factor.

$\mathbf{C}$

```

char array[10];

/* ... */

array[4]++;

```

#### Assembler

```

array: .fill 10, 1, 0

/* ... */

movl $4, %eax

incb array(,%eax,1)

```

#### Structures

$\mathbf{C}$

```

struct point

{

int x;

int y;

char color;

};

struct point first;

/* ... */

first.x = 1;

first.y = 2;

first.color = 0;

```

#### Assembler

```

/* point consists of 2 * 4 byte fields followed by

/* a 1 * 1 byte field */

first: .space 9, 0

/* ... */

/* get address of structure into a register */

movl $first, %eax

/* offset of x = 0 */

movl $1, 0(%eax)

/* offset of y = 4 */

movl $2, 4(%eax)

/* offset of color = 8 */

movb $0, 8(%eax)

```

6.2. POINTERS 45

### **Arrays of Structures**

```

\mathbf{C}

```

```

struct atom

{

short id;

char x;

char y;

};

struct atom cloud[1000];

/* ... */

cloud[4].id = 4;

cloud[4].x = 2;

cloud[4].y = 1;

```

#### Assembler

```

/* atom consists of 1 * 2 byte fields followed by

/* a 2 * 1 byte field */

cloud: .fill 1000, 4

/* ... */

/* get address of structure into a register */

movl $cloud, %eax

/* set up index value */

movl $4, %ebx

/* offset of id = 0 */

movb $4, (%eax,%ebx,4)

/* offset of x = 2 */

movl $1, 2(%eax,%ebx,4)

/* offset of y = 3 */

movl $2, 3(%eax,%ebx,4)

```

# Chapter 7

## Subroutines - Advanced

Chapter 5 introduced the basic concepts of the 'system' or 'process' stack, and the subroutine, these concepts will be expanded upon in this chapter by introducing techniques for parameter passing, local variables, and returning results.

## 7.1 Parameter Passing

The parameters of a subroutine are the values that are passed to a subroutine for it to operate on. There are two basic methods of passing parameters - by stack and by register - which may be combined to yield hybrid methods.

Parameters may be divided into the two classes, reference parameters and value parameters.

This section will cover the definition, implementation and characteristics of passing methods and parameter types.

### 7.1.1 Pass by Register

This is the simplest form of parameter passing. The information to be passed to the subroutine is loaded into registers and the subroutine called.

```

movl $1, %eax

movl $2, %ebx

call trivadd

/* ... */

trivadd:

addl %ebx, %eax

ret

```

The advantage of this form is that it permits the subroutine direct access to the parameters in registers. As registers are the fastest form of storage available to the processor this permits fast subroutines to be written.

Pure register passing is limited in the number and type of values that can be passed to a subroutine. This limitation is imposed by the number and size of available registers. There are additional costs in using register based passing. These result from the need to save values that were previously in registers before setting up for a call. Restoring the registers is necessary if the values are to be used after returning from the call.

### 7.1.2 Pass by Stack

Passing values using the stack permits greater flexibility than passing by register. Provided there is sufficient space on the stack, any type and number of values may be transferred as parameters to a subroutine using stack based passing.

Parameters are pushed onto the stack before the subroutine is called. Indexed addressing relative to the stack pointer is used to recover the values of the parameters.

```

push1 $1

push1 $2

call trivadd

add $8, %esp

/* ... */

trivadd:

movl 4(%esp), %ebx

movl 8(%esp), %eax

addl %ebx, %eax

ret

```

The stack can be represented diagramatically:

Parameters passed to a function may be of varying sizes. The following program fragment shows an implementation of a function which takes a long integer, followed by a word-sized integer, followed by another long integer.

```

pushl $1

pushw $2

pushl $3

call oddadd

addl $10, %esp

/* ... */

oddadd:

movzwl 8(%esp), %eax

addl 4(%esp), %eax

addl 10(%esp), %eax

ret

```

The stack diagram indicates the offsets and sizes of the parameters relative to the value of the stack pointer when the function is called.

In both the examples given above, the stack pointer was adjusted to point to the position it held before the parameters were pushed onto the stack. It is important to ensure that the stack pointer is pointing to a valid return address when a return is executed. Failure to do so will result in either an access violation or a jump to a location in memory where there may not be valid code.

Pass by stack has speed penalty in access to the parameters. The parameters mut be saved on the stack and later accessed by the subroutine. This time penalty aside, access by stack, provides a consistent, flexible mechanism for accessing subroutine parameters.

### 7.1.3 Pass by Value and Pass by Reference

In the preceding examples all parameters passed have been passed by value That is the value of the parameter is either loaded into a register (for pass by register) or pushed onto the stack (for pass by register). Parameters may also be passed by reference, that is the address of an item may be passed to a function, and operations may be conducted on the item *insitu* in memory.

The 'C' programming language only provides passing by value. Programmers in 'C' must pass pointers to objects they wish to modify using a subroutine. Pascal provides both pass by value and pass by reference. The following is an example Pascal code fragment:

```

procedure addtwo(var result: integer; p1, p2: integer);

begin

result := p1 + p2;

end;

{ ... }

addtwo(res, 2, 4);

Translated into assembly language:

addtwo:

movl 4(%esp), %eax

/* get p2 */

addl 8(%esp), %eax

/* add p1 */

/* get the address of result */

movl 12(%esp), %edx

movl %eax, (%edx)

/* store the result */

ret

/* ... */

pushl $result

push1 $2

pushl $4

call addtwo

add $12, %esp

```

For small data items passing by value has the advantage of providing a copy of the value to the subroutine which it may alter without destroying the value used by the calling routine. If the data item is sufficiently large, then the convenience gained is offset by the overhead of copying the data item.

### 7.1.4 Returning Results

The results of a function may be returned by using either a register or by a reference to memory. Returning results by reference is equivalent to passing an additional pass by reference parameter to a function, and using that parameter for the return value.

#### 7.1.5 Local Variables and Stack Frames

A local variable is a variable that is not visible to the caller of a subroutine but is visible to the subroutine. Local variables serve the dual purposes of reducing the amount of global storage space required for a program and providing a private storage area that a subroutine can use. Local variables are created when they are required and persist until the function exits. This ensures that the variable only consumes space when the variable is in use. Recursive routines often require a quantity of storage space in which the current state is stored. Local variables are created with each instance of a subroutine, and provide a natural location in which to store intermediate results.

Local variables are created in assembly language by reserving space on the stack after the parameters. A 'C' program fragment that generates a Fibonacci sequence as an example of a recursive program with local variables is shown below.

```

void fib(int a, int b)

{

int c;

printf("%d ", a);

c = a + b;

if (c > 50)

return;

fib(b, c);

}

/* ... */

fib(1,1);

```

An assembly language fragment using local variables reserved on the stack directly following the parameters of the function:

```

fib:

subl $4, %esp

/* reserve space for c */

/* recover the a parameter */

movl 12(%esp), %eax

call print_num

/* call fictitious print routine */

movl 8(%esp), %ebx

/* recover the b parameter */

movl %eax, 0(%esp)

/* store a in c */

addl %ebx, 0(%esp)

/* add b */

movl 0(%esp), %ecx

/* move value c into %ecx */

cmpl $50, 0(%esp)

/* test against 50 */

jge skip

pushl %ebx

/* call fib */

pushl %ecx

call fib

addl $8, %esp

/* fix the stack pointer */

skip:

/* remove C from stack */

addl $4, %esp

ret

/* ... */

/* fib(1,1) */

pushl $1

pushl $1

call fib

addl $8, %esp

```

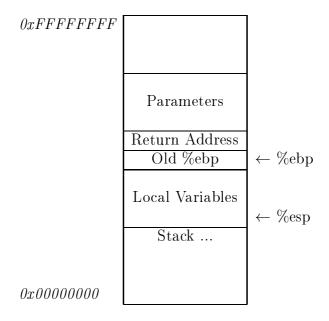

A Stack frame is a data structure on the system stack, and which provides a consistent method for representing subroutines. It allows the easy creation of local variables, and permits the use of the stack instructions push and pop.

A stack frame may be created using either the **enter** instruction or by pushing the appropriate values directly onto the stack. Stack frames are destroyed by the **leave** instruction.

The simplest form of the 386/486 stack frame is:

A stack frame uses the base pointer to keep track of the division between a functions parameters and the functions local variables. The use of the base pointer also allows the deallocation of the local variable space and any stack space used by a subroutine on exiting the routine.

Local variables may be accessed using negative offsets from the base pointer and parameters are accessible using positive offsets. Use of push and pop do not affect the base pointer, so the offsets are not affected by normal activity on the stack.

The code that forms a simple stack frame with *space* bytes of local variables is:

```

push1 %ebp

mov1 %esp, %ebp

sub1 $space, %esp

```

This is equivalent to the command enter \$space, \$0. The leave instruction may be emulated by the code:

```

movl %ebp, %esp

popl %ebp

```

Leave, restores the base pointer to its previous values.

The example Fibonacci program rewritten to use a simple stack frame:

```

fib:

pushl %ebp

/* create stack frame */

movl %esp, %ebp

/* reserve space for c */

subl $4, %esp

movl 12(%ebp), %eax

/* recover the a parameter */

call print_num

/* call ficticious print routine */

/* recover the b parameter */

movl 8(%ebp), %ebx

movl %eax, -4(%ebp)

/* store a in c */

addl %ebx, -4(%ebp)

/* add b */

movl -4(\%ebp), \%ecx

/* move value c into %ecx */

cmpl $50, -4(%ebp)

/* test against 50 */

jge skip

pushl %ebx

/* call fib */

pushl %ecx

call fib

addl $8, %esp

/* fix the stack pointer */

skip:

movl %ebp, %esp

/* destroy stack frame */

popl %ebp

ret

/* ... */

/* fib(1,1) */

pushl $1

pushl $1

call fib

addl $8, %esp

```

Using enter and leave:

```

fib:

enter $4, $0

/* reserve space for c */

/* recover the a parameter */

movl 12(%ebp), %eax

/* call fictitious print routine */

call print_num

movl 8(%ebp), %ebx

/* recover the b parameter */

movl %eax, -4(%ebp)

/* store a in c */

addl %ebx, -4(%ebp)

/* add b */

movl -4(%ebp), %ecx

/* move value c into %ecx */

/* test against 50 */

cmpl $50, -4(%ebp)

jge skip

/* call fib */

pushl %ebx

pushl %ecx

call fib

addl $8, %esp

/* fix the stack pointer */

skip:

/* destroy stack frame */

leave

ret

/* ... */

pushl $1

/* fib(1,1) */

pushl $1

call fib

addl $8, %esp

```

# Chapter 8

## **Data Structures**

The choice of the method of representation of data in a program has a major effect on the performance of the program. Data structures determine the upper bound of the efficiency of operations on data by an algorithm. Because of the importance of the method of storage of data, this chapter will be devoted to discussing the implementation of some data structures in assembly language.

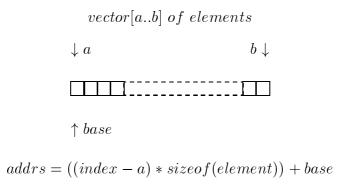

### 8.1 Vectors

A vector is a one dimensional array. The assembly language representation of an array consists of a set of equal size objects consecutive in memory. Elements of this set are accessed by multiplying the index of the required element by the size of the element and adding this to the base address of the array. The general representation is shown in figure 8.1.

The vector was introduced in the section on indexed addressing (6.1.2). Code was introduced into that section which used the inbuilt index granularities of 1, 2, 4, and 8 bytes. An example of a generalized indexing scheme which can be used for other element sizes follows.

Figure 8.1: General Representation of a Vector

```

/* calculate offset from base */

movl \$index, %ebx

subl \$first, %ebx

movl \$size, %eax

/* note that this multiply destroys the contents of %edx */

/* and leaves the result in %eax */

mull %ebx

/* add base to offset %eax points to beginning of item */

addl \$base, %eax

/* access first word of element */

movl 0(\%eax), %ecx

```

## 8.2 Arrays

Vectors are a restricted form of the general concept of an array. An array may have more than one dimension, hence, it may be indexed by more than one parameter.

The memory of a computer may be viewed as a one dimensional array of storage locations. Multi-dimensional arrays may be considered as an array of an array of one less dimension. By applying this view recursively until a representable vector has been reached allows an array of any number of dimensions to be constructed.

Two dimensional arrays will be used as an example of constructing multidimensional arrays. The concepts used in constructing and describing two dimensional arrays may be extended by induction to other multi-dimensional arrays.

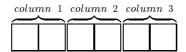

There are two ways of linearizing a multidimensional array. The first is to store the first row of the array in memory followed by each subsequent row. This is known as *row-major* form. The second method stores the columns in order, and is known as *column-major* form. (See figure 8.2 for a pictorial form).

The following section of code provides access to a row-major form 2 dimensional array of arbitrary sized items represented by the Pascal like declaration:

8.2. ARRAYS 59

Two Dimensional Array:

Row Major Form:

Column Major Form:

Figure 8.2: Major Forms

```

/* calculate size of a row */

movl $b, %ebx

subl a, %ebx

movl $size, %eax

/* note that this multiply destroys the contents of %edx */

/* and leaves the result in %eax */

mull %ebx

/* work out the relative row index */

movl rowidx, %ebx

subl $a, %ebx

/* calculate the row offset */

/* note that this multiply destroys the contents of %edx */

mull %ebx

/* store result in %ecx */

movl %eax, %ecx

/* calculate column offset */

movl $colidx, %ebx

subl c, %ebx

movl $size, %eax

/* note that this multiply destroys the contents of %edx */

mull %ebx

/* add in stored result and base to get pointer to start of */

/* element [rowidx, colidx] */

addl %ecx, %eax

addl $arr, %eax

```

### 8.3 Records

A record is a synonym for structure in the context of computer languages. Structures are manipulated by adding an offset to the base address of the structure to yield the address of the element of the structure to be altered. Examples may be found in Chapter 6.

### 8.4 Dope Vectors

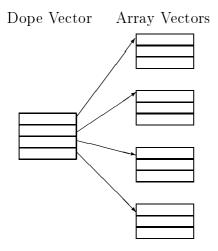

A dope vector is a one dimensional array containing the starting addresses of other objects. Multi-Dimensional arrays can be constructed using dope vectors which involves the storing the starting addresses of an array of lower dimension in the dope vector (see figure 8.3).

Figure 8.3: A dope vector

The sample code manipulates a four by four array of long words stored in row-major form using a dope vector implementation:

```

/* declarations for array in row major form */

.long r0, r1, r2, r3

.fill 10, 4, 0

r0:

.fill 10, 4, 0

r1:

r2:

.fill 10, 4, 0

r3:

.fill 10, 4, 0

/* ... */

/* retrieve address of row */

movl $rowidx, %ebx

movl dpv(,%ebx,4), %edx

/* retrieve value at column */

movl $colidx, %ebx

movl (%edx, %ebx, 4), %eax

```

## 8.5 Trees and Graphs

Tree and graph structures are built in assembly language in a manner similar to that used in the 'C' programming language. Essentially a node consists of a structure containing some data and a number of pointers to other nodes. By connecting the nodes together a tree or a graph can be built.

# Chapter 9

# **Block Structured Languages**

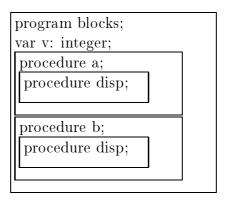

Block structured languages allow nesting and scoping of subroutines and variables. Pascal supports these features, unlike the 'C' programming language. The following simple Pascal program illustrates the concept of block structuring.

```

program blocks(input, output);

procedure a;

var

v: integer;

procedure disp;

begin

writeln('a', v);

end;

begin

v := 1;

disp;

v := 2;

disp;

end;

procedure b;

var

v: integer;

procedure disp;

begin

writeln('b', v);

end;

begin

```

```

v := 1;

disp;

v := 2;

disp;

end;

begin

a;

b;

end.

```

The program's output is 'a1 a2 b1 b2'. The structure of a block structured program may be drawn:

In Pascal, the scope of a variable is the region in which it is accessible by name to a subroutine. Variables declared in blocks of which the current subroutine is a strict subset are within the scope of the current function.

The scope of a subroutine in Pascal is the region in which a function or procedure may be called by name. Procedures and functions in the current block and blocks which are one level above the current block and contained by the current block are accessible.

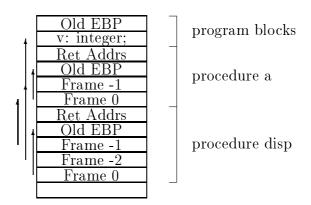

Block structured languages are supported in assembler by providing backward links in the stack frame to earlier stack frames. The **enter** instructions second parameter, **level**, determines the number of stack frame pointers that are inserted into the current stack frame to the previous stack frame. Figure 9.1 shows an example of the appearance of the stack with back pointers. The example shows the invocation of disp by procedure a.

By following back the chain of back pointers it is possible to access any variable in the scope of the current function.

Figure 9.1: Stack Frames in a Block Structured Language

# Appendix A

# AT&T Syntax

## A.1 Register Set

The 80386/80486 provides a set of general registers, segment registers, debug registers and control registers. The name and size is recorded for each register directly accessible using an **AT&T** type assembler. Note that all register names are preceded by a percent sign.

## General Purpose Registers:

| Register         | Width  | Type                     |

|------------------|--------|--------------------------|

| Name             | (bits) |                          |

| %eax             | 32     | General Purpose Register |

| %ax              | 16     | Least 16 bits of %eax    |

| %ah              | 8      | Greatest 8 bits of %ax   |

| %al              | 8      | Least 8 bits of %ax      |

| %ebx             | 32     | General Purpose Register |

| %bx              | 16     | Least 16 bits of %ebx    |

| $\%\mathrm{bh}$  | 8      | Greatest 8 bits of %bx   |

| %bl              | 8      | Least 8 bits of %bx      |

| %ecx             | 32     | General Purpose Register |

| %cx              | 16     | Least 16 bits of %ecx    |

| $\%\mathrm{ch}$  | 8      | Greatest 8 bits of %cx   |

| $\% \mathrm{cl}$ | 8      | Least 8 bits of %cx      |

| %edx             | 32     | General Purpose Register |

| %dx              | 16     | Least 16 bits of %edx    |

| $\%\mathrm{dh}$  | 8      | Greatest 8 bits of %dx   |

| %dl              | 8      | Least 8 bits of %dx      |

| %ebp             | 32     | Base Pointer             |

| %bp              | 16     | Least 16 bits of %ebp    |

| %esi             | 32     | Source Index             |

| %si              | 16     | Least 16 bits of %esi    |

| %edi             | 32     | Destination Index        |

| %di              | 16     | Least 16 bits of %edi    |

| %esp             | 32     | Stack Pointer            |

| $\%\mathrm{sp}$  | 16     | Least 16 bits of %esp    |

## Segment Registers:

| Register         | Width  | Type          |

|------------------|--------|---------------|

| Name             | (bits) |               |

| $\%\mathrm{cs}$  | 16     | Code Segment  |

| $\% \mathrm{ds}$ | 16     | Data Segment  |

| $\% \mathrm{es}$ | 16     | Extra Segment |

| % ss             | 16     | Stack Segment |

| %fs              | 16     | Segment       |

| $\% \mathrm{gs}$ | 16     | Segment       |

A.2. FLAGS 69

### Debug Registers:

| Register | Width  | Type                                         |

|----------|--------|----------------------------------------------|

| Name     | (bits) |                                              |

| % dr0    | 32     | Breakpoint 0 Linear Address - Debug Register |

| %dr1     | 32     | Breakpoint 1 Linear Address - Debug Register |

| %dr2     | 32     | Breakpoint 2 Linear Address - Debug Register |

| %dr3     | 32     | Breakpoint 3 Linear Address - Debug Register |

| % dr6    | 32     | Debug Control Register                       |

| % dr7    | 32     | Debug Control Register                       |

### Test Registers:

| Register           | Width  | Type          |

|--------------------|--------|---------------|

| Name               | (bits) |               |

| %tr3               | 32     | Test Register |

| $\% \mathrm{tr}4$  | 32     | Test Register |

| $\% \mathrm{tr} 5$ | 32     | Test Register |

| %tr6               | 32     | Test Register |

| %tr7               | 32     | Test Register |

### Floating Point Stack Registers:

| Register  | Type               |

|-----------|--------------------|

| Name      |                    |

| %st       | Top of NPU stack   |

| %st $(0)$ | Top of NPU stack   |

| %st(1)    | NPU stack register |

| %st $(2)$ | NPU stack register |

| %st(3)    | NPU stack register |

| %st(4)    | NPU stack register |

| %st $(5)$ | NPU stack register |

| %st(6)    | NPU stack register |

| %st $(7)$ | NPU stack register |

## A.2 Flags

The 80386 provides a flag register known as EFLAGS. This register contains bits which are set by the processor after arithmetic operations or which reflect the current state of the processor.

The flags are:

**AC** Alignment Check<sup>1</sup>.

VM Virtual 8086 Mode

RF Resume Flag

NT Nested Task Flag

**IOPL** IO Privelege Level (2 bits)

**OF** Overflow Flag

**DF** Direction Flag

IF Interrupt Flag

**TF** Trap Flag

SF Sign Flag

**ZF** Zero Flag

**AF** Auxiliary Carry Flag

**PF** Parity Flag

CF Carry Flag

## A.3 Assembler Syntax

This section is specific to the Free Software Foundation's GNU AS assembler. Many of the other **AT&T** type assemblers use a similar set of operations, typically a subset of these.

### A.3.1 General Layout

The assembler input is free form, requiring only that statements be separated by either a newline character or a semicolon. Character constants are not terminated by a newline or semicolon (';') character. A statement may be continued over more than one line by placing a backslash ('\') before the newline character.

Symbols may be made up of alphabetics, digits, '-', '\$' and '.'. Symbols are case significant. The special symbol '.' refers to the current address that is being assembled to.

Strings are delimited by double-quote character ("").

Numbers follow the conventions of C:

<sup>&</sup>lt;sup>1</sup>Not available on the 80386

**Decimal** Any number not beginning with a zero eg. 10.

Hexadecimal A number beginning with '0x' eg. 0xa.

Octal A number beginning with zero eg. 012.

Special characters follow the conventions of C:

```

\begin{tabular}{ll} \beg

```

$\fine formfeed$

$\t$  Tab

\ooo where o is an octal digit An octal character code.

```

\\ The '\' character.

```

\" The "" characther

Labels are a symbol followed immediately by a colon (':').

### A.3.2 Operands

Immediate operands are numbers which do not represent memory locations. These are prefaced in **AT&T** type assemblers by a dollar sign ('\$').

Absolute references are prefaced by an asterix (`\*) to differentiate them from relative references.

The size of operands are determined explicitly by the instruction, not by reference to the size of the object refered to. Opcode suffixes are added to indicate the size of the operation.

```

b Byte (8-bit)w Word (16-bit)l Long (32-bit)

```

#### A.3.3 Comments

There are two forms of comments:

- C type: Comments may be multiline and are delimited by '/\*' and '\*/'.

- Line Comment type: All characters from '#', the line comment character, to the next newline are ignored.

### A.3.4 Expressions

The following operators are available:

- Two's complement negation.

- ~ One's complement negation.

- \* Multiplication.

- / Division.

- % Modulo.

- < or << Left shift.

- > or >> Right shift.

- Bitwise Or.

- & Bitwise And.

- ^ Bitwise Xor

- ! Bitwise Or Not.

- + Add.

- Subtract.

#### A.3.5 Assembler Directives

- .abort Stop assembly immediately

- .align boundary, pad Adjust the location counter to the next boundary exactly divisible by  $2^{boundary}$ . If pad is present then this value of the bytes used in filling to the next boundary.

- .ascii strings Reserves space for and stores strings.

- .asciz strings Reserves space for and stores strings with an additional zero byte at the end of each string.

- .byte expressions Comma separated expressions are stored into the next byte.

- .comm symbol, length Declares a named common area of at least length bytes size.

- .data subsegment Assembles following statements at the end of data subsegment subsegment. The default subsegment is 0.

- .double flonums Comma separated floating point numbers are stored into the 64-bit floating point form.

- .file string The string becomes the name of the new logical file.

- .fill repeat, size, value Creates a block of repeat objects of size bytes containing value.

- .float flonums Comma separated floating point numbers are stored into the 32-bit floating point form.

- **.globl** symbol Makes symbol visible to the linker.

- .int expressions Comma separated expressions are stored into the next 32 bits.

- .lcomm symbol, length Declares a local common area of at least length bytes size. At run time the bytes of this area start off zeroed. This area is not visible to the linker.

- .line number Assigns a logical line number to the statements following.

- .long expressions Comma separated expressions are stored into the next 32 bits.

- .octa bignums Comma separated big numbers are stored into the next 16 bytes.

- .org lc, fill Advances the segments location counter to lc using fill as padding.

- .quad bignums Comma separated big numbers are stored into the next 8 bytes.

- .set symbol, expression Sets the value of symbol to expression.

- .short expressions Comma separated expressions are stored into the next 16 bits.

- .single flonums Comma separated floating point numbers are stored into the 32-bit floating point form.

- .space size, fill Fills an area of size bytes with the value fill. If fill is omitted then the area is filled with zeros.

- .text subsegment Assembles following statements at the end of text subsegment subsegment. The default subsegment is 0.

- .word expressions Comma separated expressions are stored into the next 16 bits.

### A.3.6 Memory References

Direct memory references may be made by using either a symbol, a numeric constant or an expression.

The AT&T syntax for indirect memory references is:

This may be explicitly written as:

$$\left\{ \begin{array}{l} \%cs \\ \%ds \\ \%es \\ \%ss \\ \%fs \\ \%gs \end{array} \right\} : \left\{ \begin{array}{l} No\ Displacement \\ 8-Bit\ Displacement \\ 32-Bit\ Displacement \end{array} \right\} \left( \left\{ \begin{array}{l} \%eax \\ \%ebx \\ \%ecx \\ \%edx \\ \%esi \\ \%edi \\ \%edi \\ \%ebp \\ \%esp \end{array} \right\}, \left\{ \begin{array}{l} 1 \\ 2 \\ 4 \\ 8 \end{array} \right\} \right)$$

The effective address of a memory location is calculated:

$$\left\{ \begin{array}{c} \%cs \\ \%ds \\ \%es \\ \%es \\ \%fs \\ \%gs \end{array} \right\} + \left\{ \begin{array}{c} No\ Displacement \\ 8-Bit\ Displacement \\ 32-Bit\ Displacement \end{array} \right\} + \left\{ \begin{array}{c} -\\ \%eax \\ \%ebx \\ \%ecx \\ \%edx \\ \%edx \\ \%edx \\ \%edx \\ \%edi \\ \%edi \\ \%ebp \\ \%esp \end{array} \right\} * \left\{ \begin{array}{c} -\\ 1\\ 2\\ 4\\ 8 \end{array} \right\}$$

If the segment modifier is not included then the instruction uses the default segment. If the displacement is not included then a displacement of zero is assumed. The valid forms of the index section are:

```

(base, index, scale)

(base, index)

(base)

(, index, scale)

(, index)

```

# Appendix B

# Instruction Set

### B.1 Layout

The instructions to be used in these lab classes are provided in this chapter. The description of each instruction is divided into 6 components. The ADD instruction is presented, with commentary, as an example.

Each instruction is documented for an AT&T style of assembler.

#### B.1.1 Title lines

#### ADD Add

This line contains the mnemonic for the instruction on the left hand side and a description of the function of the instruction at the right.

### B.1.2 Type & Compatibility

| Flow | Int | Float | Multi | IO |

|------|-----|-------|-------|----|

|      | X   |       |       |    |

| OpSys |

|-------|

|       |

| 386 | 387 | 486 |

|-----|-----|-----|

| ×   |     | ×   |

This set of boxes classifies the type of the instruction and the processors with which the instruction is compatible.

The type compatibility boxes are:

**Flow** Flow of Control - Instructions which may cause execution to change to a location other than the next instruction.

Int Integer - Instructions that operate on integer values.

Float Floating Point - Instructions which operate on floating point numbers.

Multi Multi-Segment - Instructions which operate on more than one segment.

The operating system box (OpSys) is checked if the instruction is not used by applications programs.

The processor compatability boxes are:

- 386 i80386 This box is checked if this instruction is available on the 386 processor.

- 387 i80387 This box is checked if this instruction is available on the 387 numeric processing unit (NPU). The floating point coprocessor for the 386.

- 486 i80486 This box is checked if this instruction is available on the 486 processor.

#### B.1.3 Formats

#### Formats:

AT&T

ADD imm, mem

ADD reg, mem

ADD imm, reg

ADD mem, reg

ADD reg, reg

The AT&T column is used for AT&T type assemblers. Listed in the column is the mnemonic for the instruction and the valid types of operands for that instruction.

The operand types are:

imm An immediate value.

m14/28byte The address of a memory location extending over 14 or 28 bytes

m16int The address of a memory location that represents a 16 bit integer.

m16real The address of a memory location that represents a 16 bit real.

m2byte The address of a memory location extending over 2 bytes.

m32int The address of a memory location that represents a 32 bit integer.

m32real The address of a memory location that represents a 32 bit real.

**m64int** The address of a memory location that represents a 64 bit integer.

m64real The address of a memory location that represents a 64 bit real.

m80dec The address of a memory location that represents a 80 bit decimal.

m80real The address of a memory location that represents a 80 bit real.

m94/108byte The address of a memory location extending over 94 or 108 bytes.

mem The address of a memory location.

ofs A signed offset from the current memory location.

B.1. LAYOUT 79

**ptr** A pointer. The address of a value which consists of a selector and a the address of a memory location.

reg Any register.

reg16 A 16 bit register.

reg32 A 32 bit register.

sreg A segment register.

**ST** The top of the NPU stack.

ST(i) The ith element of the NPU stack.

#### **B.1.4** Psuedo Instructions

#### Pseudo:

AT&T

ADD src1, dst

The instruction is followed by pseudo operands. The pseudo operands are used in the description of the instruction that follows this section. The pseudo instruction and operands is used to group different versions of the same instruction which have the same form.

### **B.1.5** Description

#### Description

This instruction adds two integers - src1 and dst - leaving the result in dst. The flags are set accordingly. If src1 is an immediate byte value then it is sign extended to the size of dst before the addition.

This section contains a short description of the function of the instruction and any warnings relavent to its use.

### B.1.6 Flags

#### Flags:

| OF | SF            | ZF | AF | PF |

|----|---------------|----|----|----|

| M  | M             | M  | M  | M  |

| CF | $\mathrm{TF}$ | IF | DF | NT |

| M  |               |    |    |    |

This section lists the flags consulted or altered by the instruction. The codes are:

Blank Flag is unaffected by instruction.

**T** Flag is tested by instruction.

M Flag is modified by instruction depending on the operands.

- 1 Flag is set by instruction.

- ${f 0}$  Flag is cleared by instruction.

- ${f U}$  The instruction's effect on the state of the flag is undefined.

### **B.2** Instructions

### AAA ASCII Adjust after Addition

| Flow | Int | Float | Multi | IO |

|------|-----|-------|-------|----|

|      | ×   |       |       |    |

| OpSys |

|-------|

|       |

| 386 | 387 | 486 |

|-----|-----|-----|

| ×   |     | ×   |

Formats:

AT&T

AAA

Pseudo:

AT&T

AAA